This post will discuss a Low-Noise-Amplifier (LNA) for measurement of voltage regulators and other low noise low impedance sources. The design target had a few requirements, including:

– High gain (X1000/60dB as a minimum)

– High BW (1MHz)

– Low input referred voltage noise (<1nV/rt(Hz))

There are multiple approaches to designing such an instrument, and each designer has his own preferences based on his requirements and experience. I chose to design something that would fit my needs, which would also be discussed in this post.

Lets start with some background. In a past series of posts I’ve shared the design and measurements of an audio measurement pre-amplifier, meant mostly for audio equipment and audio frequencies. That was a very versatile pre-amplifier which tried to do everything. This included a high input impedance (100Kohm), balanced input, very wide range of gain options (-40dB/-20dB/0dB/+20dB/+40dB/+60dB), high linearity (see here for measurements), and low input noise (measured at <7nV/rt(Hz) on the high gain ranges). It included an internal RMS->DC converter and a panel meter to display the RMS value.

It was (and still is) a very capable tool, and I use it extensively, both for projects I post on this blog, and other unrelated measurements.

However, this tool isn’t optimized for one single use, therefore, if we were to target one single use case, and reduce the requirements in some aspects, we could benefit in others. This was the case for some measurements I wanted to perform in the recent past, where I’ve had no need for high input impedance, nor high linearity. I needed to measure noise of a few fairly low impedance and very low noise devices, including LDO’s as well as additional reference circuits I’ve built.

The list of requirements was therefore compiled according to these needs:

– +60dB/+80dB gain

– 1Hz-1MHz -3dB BW

– Low input referred noise at <1nV/rt(Hz) wide-band noise

– 1Kohm input impedance

The gain target is fairly straight forward to understand, as we always want the gain to be high enough to make it useable with additional instrumentation down the line. My setup is completely fine with +60dB only, but adding some optional gain on top of that will make it more versatile if this will ever be needed.

For the BW requirements, this is extending beyond what most people use for LDO measurements (100KHz typically). However, I’m measuring more than just LDO’s with this tool. My measurements are actually limited to 5Hz-10Hz in the low end, and ~300KHz on the high side, but I’ve decided to add some margin on top of that. Adding lower cutoff frequency is always possible if desired; either by modifying the capacitors inside the amplifier, or by adding an external filter, or even doing this in DSP in the scope/other test instrument.

The input noise requirement is derived from some of the LDO’s I was measuring, they were using the LT3042 which has a spec of 2nV/rt(Hz) at its optimal frequency of 10KHz (slightly higher across most of the frequency range). I wanted to be at least 6dB better than this, but final design is 8dB lower than the LT3042 (0.8nV/rt(Hz)).

For comparison, the 0.8nV/rt(Hz) input referred noise, is equivalent to the thermal noise of a 40-ohm resistor at room temperature (300K). Integrating the noise in the 10Hz-100KHz BW, results in 0.25µVrms integrated noise.

The input impedance seems somewhat high at first, the 1Kohm resistor is obviously producing far more noise than the input referred noise of this LNA. This is because from the LNA point of view, the 1Kohm is placed in parallel with the output impedance of the DUT, which would make it insignificant when measuring a low impedance DUT. The reason I wanted to have a 1Kohm input impedance is to allow measuring source of higher impedance which for some of my experiments was on the order of 100-ohm or over.

Figure 1 shows the schematic of the pre-amplifier. It consists of an isolated switching module (2 of them actually) followed by some filtering and LDO’s as the power section. A 3-stage amplifier, and an output buffer. There is an additional (optional) output limiting circuit, as well as an overload detection circuit.

Lets go over the circuit in a bit more detail, starting with the signal path which is our main point of interest. R20 is an optional resistor (1-10Mohm for instance) to discharge the input capacitor when not in use to prevent it from storing charge for a very long time. C1/C2 offer AC coupling at the input, with fc of 0.48Hz. C2 provides most of the capacitance here, and C1 is there to bypass it at higher frequency where C2 is no longer effective due to parasitic inductance. R3 is a high power resistor meant to handle (and limit) inrush current when the input voltage is ramping up/down. D1/D2 clamp the input voltage to the first amplification stage to safe values. R3 is one part when significant tradeoff exist. Choosing lower value is of interest for the sake of noise, but higher value is desired to limit inrush current and power dissipation. For instance, the 10-ohm value chosen, contributes 0.4nV/rt(Hz) input referred noise on its own, and inrush current peak when connecting a live 10VDC input source would be on the order of 1A.

Moving on to the first gain stage (U1). It uses the ADA4898-2 op-amp, which is a very low noise amplifier. To reduce its noise further, 2 such amplifiers are used in parallel and combined after the gain stage. To keep noise low, the feedback resistors use very low values, and the gain is set to 30dB to make noise contribution of following stages negligible.

The second stage (U2A) has additional gain which can be trimmed by a few % in each direction to compensate for resistor tolerance. This stage offers additional 30dB of gain for a combined gain of 60dB across the first 2 stages. Here higher value resistors can safely be used due to the high gain of the first stage.

The third stage (U2B) is once more AC coupled with fc of 0.16Hz, to remove offset accumulated by the previous stages due to their high gain. There is optional DC offset trimming at this stage, but I would consider it of no practical use and it can be left unpopulated, as the maximum offset is already very low without trimming (20mVDC). The third gain stage has selectable gain between 0dB/20dB (X1/X10), according to the needs of the specific measurement setup and DUT.

Finally, there is an output driver stage (U8). This stage has a gain of unity (0dB/X1), and uses a difference amplifier structure. This is meant to reduce potential ground noise effects by moving the output voltage to be referenced to the output ground instead of input ground. A ground loop breaker completes this circuit limiting the maximum voltage difference between the ground nodes to safe values. This entire structure is optional, and can be eliminated by shorting R33/R34, which would allow leaving D7/D8 as well as U8/R35/R36/R37/R38 unpopulated. This will short the two ground nodes and will make U2B the output driver amplifier. I’d like to note that this way of limiting ground noise isn’t ideal, and there are other more robust ways of doing this. However, as is, its already quite useful, and has the benefit of being simple to implement.

There is optional output limiting circuit located at the output, which is currently set to ~5.5V hard limit (it will start saturating the output at slightly lower value). This is something that can be omitted if desired, or adjusted for a different voltage by replacing D3/D4 to the desired voltage value.

U3A/U3B form a window comparator which would light up an LED if the output voltage is approaching the set value, in this case +/-4.5V. This value can easily be adjusted by R15 to any desired value. Therefore, if you modify the output limiting, or decide to omit it, you can (should) adjust R15 to the desired value. R15 should be set as:

If we substitute the values of parts in the schematic this will reduce to:

For instance, for the peak voltage I’ve defined as a target by default (4.5V), this will results in R15=47.37Kohm.

Moving to the power supply section, it is far more straight forward. Input voltage is 5VDC as I typically use or all my projects, to power it from a USB power brick I have on my bench connected to all these little instruments. This is followed by a power switch, a resettable fuse, and reverse polarity/over voltage protection zener D10, with some decoupling. For the isolated DC-DC modules I chose the IES0105S09 modules I’ve used successfully in a different board I did in the past where I didn’t observe any residual noise from its switching, although it was meant for lower frequency than this project, and not quite as low noise as this one. So this is definitely a risky choice, and one that will have to be measured afterwards. The decision to go with 2 isolated modules instead of a single dual output module is to allow use of a single polarity LDO at the output instead of a negative LDO for the negative rail. The isolated DC-DC modules are followed by a CRC filter to improve PSRR and effectively provide almost no ripple at the input of the following LDO’s. For the LDO’s I chose the ADP7118 5V variant.

This LDO choice deserves some additional attention as its not at first obvious.

– One question would be, why not use an absolute over-kill LDO such as the LT3042?

The simple reason is that there is no need for that. If you consider the noise of the 7118, and translate it to the input of the LNA, it will have basically no effect there. So if there’s no improvement in performance, why opt for a more expensive part.

– A second question might be why not use the “adjustable” variant of the 7118 instead of the 5V variant?

This is because the 5V variant output noise is very close to that of the “adjustable” variant. Therefore, its best to start with the 5V option, and adjust that to the desired value with reduced gain, instead of a lower reference adjustable variant and use a higher gain value.

– Next question might be why not add bypass to the feedback network of the LDO to reduce noise further?

This can actually improve supply noise somewhat, but this is a very marginal improvement as we are already operating the LDO with limited division in the feedback network. Combine that with the fact that the noise of the LDO is far below the input referred noise of the LNA, and the “effort” to bypass the LDO feedback correctly is basically of no practical use.

Finally, I must admit the ADP7118 looked like an interesting LDO for other projects I’m considering for the future, so I chose to use this LNA as a test case for it.

I’ve ordered the PCB, as well as PCB’s for the panels of the case, to allow me to assemble a prototype and measure its performance. The high value of capacitance, and voltage rating I chose for C2 meant I had to use tall capacitors. This in turn called for a slightly higher case than the one I’ve used for the small projects I did in the past such as this/this/this. I found a similar case with identical width/depth which was 15mm higher, and seemed like a perfect match. It was even similarly priced, so I’ve ordered one to try it out.

After a long wait for the parts to arrive (supply issues nowadays affect DIY projects too unfortunately), I go the unit assembled and was finally able to start some measurements.

Before measuring, I’ve started with trimming the gain for +60dB via RV1, and while at it also adjusted the output DC offset to <1mV via RV2. This last step is optional as its already quite low to begin with, but I’ve added it for completeness. Note that because of the way the ground loop and the final stage around U8 are implemented, R34 actually alters the gain if you are using a floating DUT. Therefore, this value is kept low in relation with R35. With the current values, this will results in <0.5% gain difference between a floating DUT, and one that is connected to the same ground as the following test instrument after the LNMP. As I’ve mentioned earlier, this is the “price” of this simple implementation, which I consider a non-issue for my use.

There are a few measurements I want to cover for this pre-amplifier. First are functional measurements such as output clipping value, and overload detection thresholds, to make sure these match my calculations. Next, I’d like to measure the input noise parameters, and frequency response. Finally, I’d like to measure linearity. While this isn’t a requirements from such an instrument, my hand calculations show this shouldn’t be a limiting parameter and linearity should also allow measuring additional signals other than simply noise. I’d like to verify that for completeness.

Lets start with the functional measurements. I’ve monitored the output signal from the LNMP, while gradually increasing the input signal amplitude. The overload protection LED lighted up at an output amplitude of 4.4V (Figure 6 below). I’ve increased this further to see the clipping behavior, as shown in Figure 7 below.

Moving on to the frequency response, I’ve plotted this for 0.1Hz-5MHz, in 1-2-5 jumps in the figure below. The normalized frequency response is shown for both gain settings, +60dB and + 80dB. The Gray line marks the -3dB points, which start at <0.5Hz, and end at 1MHz.

So far things were going well, too well. Something must go wrong, and sure enough, something did. As I moved to noise measurements, I’ve noticed that while the integrated noise was not too far from expectations (2-3dB high for overall integrated noise), I was able to see some hints of dominant tones in the waveform. This is something that is easier to see in the FFT with the scope, as shown in the figure below.

This shows an FFT from 0Hz-5MHz, with 500KHz per division. As is clearly visible, there are tones there at just over 250KHz and its harmonics. In fact, its clear there are 2 such tones in close proximity. This already explains what the source of this noise is, the switching modules generating the isolated rails. This is easy enough to confirm, and indeed, replacing the +/-9V rails with external DC rails from a lab PS removed these tones completely. Much of this noise (although not all of it), is coupling because of the high impedance at the input for the circuit relative to earth. This is a side effect of the ground-loop-breaker included in the circuit. Therefore, while the source of this is well understood, fixing it will call for some modifications.

First, I’ve decided to short the ground loop breaker (R34), as the benefit it has in some situations, is out-weighted by this switching noise coupling from the power section to the input section. This improved things noticeably, but not enough for me to be happy with this as a whole. A complete solution would call for additional changes to the structure of the circuit, which I cannot properly implement on the existing PCB. Therefore, I’ve decided to “re-propose” this LNMP somewhat. While one use case I’ve had called for 300KHz BW as mentioned earlier in this post, more often than not, this will be used for linear-regulator noise/ripple measurements. Thankfully, these are typically only spec’d for 10Hz-100KHz, which falls well below the first spur from the DC-DC modules. Therefore, I’ve modified the feedback capacitors across all stages, and reduced the BW to slightly over 100KHz. This attenuates these spurs, so even when measuring with a wide-band voltmeter, the RMS value is hardly affected by this.

The revised schematic, after all these modifications, can be seen in figure 10 below. The resulting frequency response is included in figure 11. The revised frequency response has its -3dB point at ~110KHz.

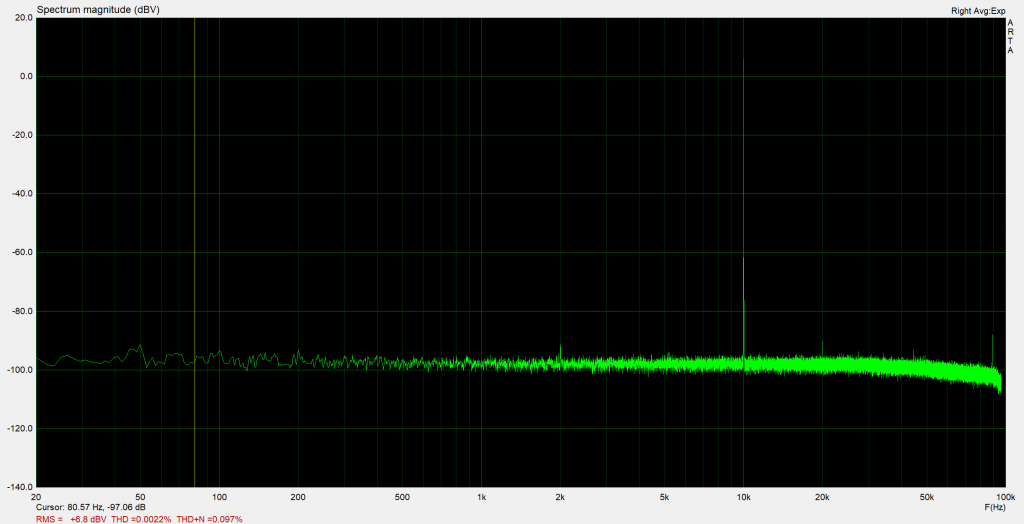

Next I had to measure the input referred noise of this LNA to make sure it meets calculated values. This was done by connecting it to the audio-measurement pre-amplifier, and observing its spectrum, as well as taking the reading from the panel mounted RMS voltmeter. The BW of the RMS meter is far higher than that of the LNA, therefore, the noise-BW can be calculated from the frequency response of the LNA. The spectrum of this measurement can be seen in figure 12. This measurement was taken with the LNA set to +80dB gain, and the audio-measurement pre-amplifier set to +40dB gain. So overall, this is with +120dB of gain. The reading on the RMS meter divided by the gain would result in 230nVrms. Divide this by the noise-BW of the reading, and the resulting noise density is 0.73nV/rt(Hz), which is almost 1dB lower than the calculated values. There are a couple of additional points of interest in this measurement, such as the 50Hz pick-up which can be observed. It is quite low in amplitude (~5nVrms input referred). This is indeed coupling from the workbench, and isn’t a residual from the power-supply (was verified by running it from a power-bank). It can be improved by placing all the connected parts (including DUT) in a shielded case during measurement. The other noteworthy point is that we barely see any change at lower frequencies where flicker (1/f) noise might be of interest, which matches the specification of the ADA4898-2 op-amp. At even lower frequencies there is a DC-block filter implemented down the chain so we cant trust the figure as we go much lower than 10Hz in this measurement.

To put the LNA to test, I’ve connected a DUT in the form of a 1.2VDC regulator built around a LT3042 ultra-low noise regulator. This was on another PCB I’ve designed in the past, so the DUT board isn’t limited to just this regulator, but it does follow the guidelines of the LT3042 datasheet (with 22uF filtering capacitor for ISET pin), and has a SMA connector to allow monitoring the rail. The DC voltage (1.2V), the DC current (<30mA), and the output capacitance (~25uF overall), aren’t identical to the values of the test circuit used for noise measurements by LT in the LT3042 datasheet, but I expect similar performance with small difference. The measured spectrum can be seen in figure 13. The white noise is now about 10dB higher than with not DUT connected, which has a total integrated noise of 720nVRMS. Once you subtract from it the total noise of the LNA on its own, we have ~680nVRMS as the integrated noise of the LDO. This is approximately 15% lower than the figure in the LT3042 datasheet, although there a smaller 4.7uF capacitor was used, and a higher output current of 200mA was drawn. Therefore, these numbers are in good agreement. We can also see the noise starts rising somewhat below 1KHz, and reaching ~20dB higher than the white noise at 10Hz. This is also in good agreement with the datasheet figure for the case of CSET=22uF as used in my DUT. What’s more, we can calculate the white noise value (using the total amplifier + measurement setup gain of 120dB, and the processing gain due to the bin size used in the FFT below being ~1.5Hz), and we will get a figure of 2nV/rt(Hz). Once more, this is all in good agreement with the datasheet plots, which is excellent news.

Next I wanted to measure the linearity of the amplifier, just for completeness. For the first stage around the ADA4898-2, I’ve used X7R capacitors for BW limiting during modifications. This is because I didn’t have a 3.3nF capacitor of NP0/C0G type. However, this first stage operates with limited swing (100mVrms at most), which eases the linearity requirements out of these capacitors. I’ve measured at 10KHz, although this might degrade somewhat at higher frequencies (up to 50KHz, after which the 2nd harmonics will get attenuated as well). I’ve used a 1K:1R divider at the input to the pre-amplifier, to attenuate the signal before amplification by 60dB setting. The resulting spectrum is seen below. THD is <0.002%, but this also happens to be the distortion at the output of the generator. Therefore, all we can conclude is that at +60dB setting the distortion is <0.002% at 10KHz.

Next I repeated this at +80dB setting, but attenuating the output of the generator by 20dB, and using the same 1K:1R divider. The LNA output is shown if figure 15. This time, the input to the LNA had lower distortion than the output, so we can trust we are seeing the limits of the LNA. So at 10KHz, +80dB gain setting, the LNA has a THD of ~0.002%.

That is all for this post. The LNA I’m ending this post with isn’t quite the one I’ve imagined at the start. However, this is still a capable little unit, that can measure the noise of even the most demanding voltage regulators, as was demonstrated.

The revised list of specifications would be:

– +60dB/+80dB gain

– 0.5Hz-100KHz -3dB BW

– 1Kohm input impedance

– Input referred voltage noise 0.8nV/rt(Hz)@1KHz, 1nV/rt(Hz)@10Hz

– Input referred current noise 5.3pA/rt(Hz) including input termination resistor noise

I might revisit this in the future with a wide-band LNA that will meet the complete 1MHz target as was set in the start of this post. When (if) I do, I will make sure to update the blog to include the information.

Hey! I really enjoy your content, it is super informative and easy to read.

I have one question related to this topic.

I was wondering what does it take to make it running at high frequencies? Maybe a battery powered supply and a simple op amp rail splitter?

It would remove anything related to the low frequency noise and would improve the total noise level of the system.

Is it only the PS problem or is there anything else to take care of?

Kind regards,

GP

Hi GP,

Thanks for you feedback, glad this post was of interest to you.

The first question I would ask as a follow up to your question, is what number do you have in mind when you say “high frequency”? 🙂

Looking at the 1MHz -3dB I’ve set as my original interest point, the switching noise of the DC-DC modules is the limiting factor, as my measurements have shown. Replacing this with a higher voltage input to the unit, so no internal voltage boosting would be needed is one possible way of extending usable BW.

Another option would be moving to a larger case size so that more physical distance can be put between the switching parts and the sensitive analog portion of the circuit. Improved board layout, and perhaps even a shielded case for the first 1-2 stages can also be experimented with as a way to improve this.

If you were to go beyond 1MHz, with the gain set at each stage of the current design, you will run into GBW limitation of op-amps. This would call for reduced gain to extend BW, which is also a viable option for many applications.

However, as with all high gain circuits, the actual board layout is of significant importance. For instance, if there is any noticeable parasitic coupling from one of the later stages back to the input stage (1st amplifier), this can result in excess positive loop gain that might render the circuit unstable. This could creep in through direct coupling (capacitive for instance), or via the supply rails, or perhaps other mechanisms. This would become more of an issue at higher frequencies, so something to watch out for and verify if you push BW higher.

BR,

Anatoli.

Can you use this amplifier to measure the noise of an LTZ1000A 7V reference zener?

The reference zener noise is only relevant at very low frequency, any AC component would be filtered out in practical implementation. For such extremely low frequencies, a DC coupled amplifier is more suited, with a low frequency LPF.

You must AC couple the primary voltage because you are trying to measure microvolt noise on top of a ~7 VDC rail. And yes, I’m trying to measure low frequency noise from .1Hz -100Hz max.

Reference noise is interesting at lower frequencies, 100Hz is quite high frequency for a DC voltage reference in practical use case, and 1Hz not low enough. If I were to go to much lower frequencies than this currently does, I would not AC couple the input, it’s not a must at all. Instead I would modify the feedback network of the amplifier. 7V is low enough to be able to DC couple the input with the appropriate rail which can be beneficial. This would also allow for higher input impedance which can be useful when measuring noise of diodes at limited quiescent current.

As for your original question, just have a look at the datasheet of the LTZ1000, its white noise density (which dominates in the frequency band you’ve mentioned) is on the order of 100nV/rtHz depending on current you use. This is noticeably lower on the pre-amp.

Yes, I did say .1 Hz, you are correct, the low frequency noise dominates. If you use an LT1013 buffer, the zener noise is the dominant factor in the circuit. That’s why a 2 pole lpf buffer circuit is in many reference IC applications circuits.

If you’d like to push the corner frequency to .1Hz or lower by using the same structure, you will need to increase the input coupling capacitor value noticeably, and make sure you let it settle completely before measuring. If your zener is biased by a low current the slewing can take a while before it starts linear settling. That’s one reason I would implement things different for lower voltage/current applications.

Once you are settled the noise of the preamp won’t be an issue compared to the zener.

Thank you for your comments.